# Micro/Nano-electronics Manufacturing Research at CCNI

Max O. Bloomfield, Christopher D. Carothers, Angel Garcia, Kenneth E. Jansen, Saroj K. Navak Assad Oberai, R. Catalin Picu, Ken Rose, Mark S. Shephard, and Tong Zhang

Computational Center of Nanotechnology Innovation JCCNI

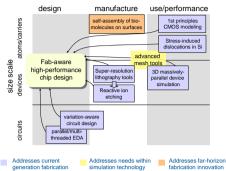

## Virtual Nanofabrication

- Nanofabrication requirements constantly changing

- More aggressive designs in microelectronics and MEMS

- Advances in biosensors and biomimetics

- •Easy to write down a design, difficult to fabricate

- •Must fabricate not one unit, but billions of units (perhaps 500 billion distinct features on a single 300 mm wafer) reliably and economically Multiple processing steps are chained sequentially, multiplying variability

- ·Simulation of the multi-step fabrication process

- Increased optimization of process flows

- Understanding of manufacturing variability and yield

- Feedback to designers

in manufacture

- -Performance simulations on as fabricated structures, rather than as

- -Develop increasingly fab-aware design rules (DFM/DFY)

# The Micro/Nanoelectronics Simulation Vision

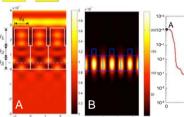

Tight coupling of CAD, meshing and finite element software Drive numerical solution with a gradient-based optimization loop to extract grating

Reducing feature size in semiconductor

In holographic lithography near-field phenomenon is predominant

with low dispersion error

Solve Maxwell's equations using a time domain-based, explicit, finite-element code

manufacturing has made the modeling of

underlying physics critical.

In projective lithography simple biases not

Projective Lithography Holographic Lithography

Schematic of two paradigms of lithographic pattern transfer: (top) Projective lithography in which a pattern on a mask is reproduced directly in a photoresist layer. (bottom) Holographic lithography in which a grating produces an interference pattern to produce a secondary mask.

Optimization for Super-resolution Nano-lithography

# Stress-Induced Dislocation Formation in Silicon Devices

- At 90 nm and below, devices have come to rely on increased carrier mobility produced by strained silicon.

• How much strain can be built into devices before processing variation and

- thermo-mechanical loads lead to dislocation nucleation?

- Concurrent atomistic and continuum simulations, using continuum error estimators to adaptively run molecular dynamics and statics simulations

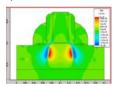

(left) Three-model multiscale simulation of deformation due to nanoindentation. Red/green (etc) Time-incuter insulaciaes simulation to deformation use to trainoritentation. Recipiers are atomistic simulation, blue is non-linear continuum simulation, and transparent is lineal elastic. (right) TSupreme4 simulation of a PFET device, showing yy stresses due to material properties mismatch. Combining atomistic simulations with this type of continuum simulation can give insight into how stress concentrations breed device-killing defects.

## Advanced Meshing Tools for Nanoelectronic Design

### Motivation

- Numerical methods within device simulation have changed little within the last 30 years, but devices have become increasingly complex

- Problem sizes and complexities are quickly out stripping the ability to solve.

### Approach

- Local refinement, local adaptivity can help carry the computation resources further. "More bang for the buck.

- Leverage existing tools to support FEMbased CCNI projects, such as advanced device modeling. Introducing extensions to meet specific

- needs. At right is shown a mesh of a single stage of a ring oscillator used in capacitance calculations ~200k elements, with conductors not shown in mesh for illustration.

## Sample Optimization of Grating

# В

# First-principles Simulations for Device Performance Modeling

- Dopant segregation and defect evolution phenomena at silicon interfaces are important for CMOS technology, particularly with high-k gate devices.

- Current process modeling are typically based on empirical parameters: needs to be obtained from first principles at nanoscale

# Approach

• First principles methods: Density functional theory (DFT), PBE functional (GGA)

• Focus on various dopants, including B, P, As, F, Ge in Si/SiO2 and SiOxNy

U→N

accurate description of defects at interface

333 Si atoms + 189 O atoms

(left) Schematic of first principles calculation of conduction in a solid. (right) 422 atom structure used to compute the effect of dopants on conduction.

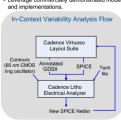

# Variation-Aware Circuit Design

## Motivation

- There exists a need to characterize the effects of manufacturing variation on final-produce performance and inform the design process.

·HO

- performance and inform the design process. Approach:

Create a parallelizable simulation infrastructure for scheduling and running CMOS fabrication process simulation and device modeling tools. Leverage commercially demonstrated models

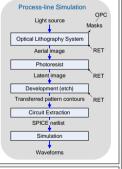

# Feature-Scale Modeling of Reactive Ion Etching (RIE)

Motivation

adequate

Approach

- Motivation

Transfer of design pattern to wafer is a two-step process: lithography and etch. Of these, etch is the less wellunderstood step.

- Can we do for etch with OPC has done for lithography? Approach

- Feature scale models operating on reature scale models operating on device-sized groups of resist contours, producing cross-sections and 3D representations of etched

- Physically based models, accounting for ballistic transport and chemical

- mechanisms at vapor-solid interfaces. structures to practical times

ion and radical fluxes

Schematic of ballistic transport and reaction model of reactive ion etching on a feature scale. Reactive species are transported to openings in the patterned mask, free from significant homogeneous collisions or reactions on the feature length scale.

Current State of Physically-Based RIE Simulation

# Self-Assembly of Biomolecules on Surfaces

- Need to explore options for sub-nanometer patterning, including self-assembly Biopolymer self-assembly can generate structures with sub-nm spatial order and molecule-level addressability, but typically occurs in solution

- Extend RPI expertise in biopolymer interactions with soft surfaces (peptide-lipid membrane) to rigid substrates of technological interest

Basic science research of interest to both IBM and RPI

## Open Questions

- what attributes determine the quality and type of ordering when multiple copies are adsorbed on various types of surfaces

- what levels of registration and dimensional control are possible in bio/nano

(left) Protein adsorption on lipid bilayer (right) Toroidal pore formation on a DOPO

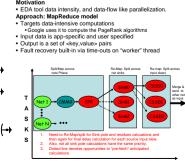

# Parallel EDA tools: Using MapReduce to Schedule RICE4

Most process codes do not do Most process codes do not complex chemistry, using sticking factors or Monte Carlo (or both). Allowing for non-linear chemistry lets you do RIE simulation over a larger range of process conditions

As an example, the simulation on the right uses a generic reactive ion mechanism with diffuse, reactive neutrals and directional ions [1]

Neutral adsorption  $X(g) +^* \rightarrow X^*$

Ion adsorption  $X^+ +^* \!\! \to \!\! X^*$ Ion-assisted etch

S+nX\* →SX. + n\* Traditionally this method scales poorly. By necessity, this example is shows a low aspect-ratio, single feature, in a low porosity substrate.

cut away view or reactive for each of an aspect ratio 1.4 via into a dielectric substrate with 7% porosity, and complete selectivity with respect to the underlying